INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING ol. 4. Issue 6. June 2016

# Design and Analysis of Data Path Elements using Low Power State Retention Technique

Mr. Pankaj R. Bansinge<sup>1</sup>, Mrs. S. R.Bichwe<sup>2</sup>

M.Tech Student, Department of EE, K. I. T. S. Ramtek (M.S.), India<sup>1</sup>

Assistant Professor, Department of ECE, K. I. T. S. Ramtek (M.S.), India<sup>2</sup>

Abstract: Most of the portable systems, such as cellular communication devices, and laptop computers operate from a limited power supply. The extension of battery-based operation time is a significant design goal which can be made possible by controlling the leakage current flowing through the CMOS circuit. Leakage power loss is critical in CMOS VLSI circuits as it leaks the battery even when the devices are in idle state. In this work a new circuit technique called LPSR technique is proposed to reduce threshold leakage power as well as total power in CMOS circuits. This proposed technique reduces maximum amount of leakage power during deep sleep mode, maximum power during dynamic mode and a provision of preserving state in low power sleep mode. Finally earlier well known techniques for leakage reduction and state retention are compared with this technique. Circuit designing, simulation and low power performance evaluation is done using CMOS technology files in Tanner EDA tool.

Keywords: Dynamic Power, Leakage Current, Low Power State Retention (LPSR), Power Dissipation, State Retention, Static Power.

## I. INTRODUCTION

all over the world today, the battery-powered electronic threshold leakage current for VGS < VT is given by, system forms the backbone. To maximize the battery life, the tremendous computational capacity of portable devices such as mobile phones, notebook computers, hearing aids etc. has to be realized with very low power requirements. The power dissipation has become a very critical design issue due to device miniaturization and rapid growth towards wireless communication. The larger the battery lasts; the better is the device. The power dissipation has not diminished even with the scaling down of the supply voltage. The technology scaling resulted in the use of lower power supply voltage for CMOS circuits which has an associated effect of lower threshold voltages to enhance performance. As the transistors cannot be switched-off completely, lower threshold voltage results in exponential rise in leakage current [1]. Since the channel length for the successive technology generations is reducing, threshold voltage and gate-oxide thickness are also being scaled down to keep pace with the performance. The total power dissipation includes dynamic and static components.

The dynamic power consumption is mainly due to the charging and discharging of the capacitance and short circuit current. Dynamic power is directly proportional to the square of the supply voltage. Therefore, dynamic power reduced in a quadratic manner when the supply voltage (VDD) is reduced.

Leakage power is dependent on the leakage current flowing in the CMOS. The components of static power dissipation are sub-threshold leakage, gate oxide leakage, junction leakage, gate induced drain leakage, and punch circuit. through leakage. In CMOS inverter ideally current flows from source-to-drain, when VGS > VT. In real transistors proposed in this paper to reduce leakage power and total current does not abruptly cut-off below threshold, but

In the increasing market of mobile hand-held devices used drops off exponentially as given by equation (1). This sub-

$$I_{DS} = I_{DS_0} e^{(V_{GS} - V_T)/(nV_T)} [1 - e^{(V_{DS}/V_T)}]$$

(1)

Where,

$$V_{\rm T} = V_{\rm T_0} - \eta V_{\rm DS} + \kappa \left[ (\phi_{\rm S} + V_{\rm SB})^{0.5} - (\phi_{\rm S})^{0.5} \right]$$

(2)

In above equations,  $I_{DS0}$  is current at threshold,  $\gamma$  is the body effect coefficient, n represents the effect of drain-tosource voltage (V<sub>DS</sub>) on threshold voltage, n is the subthreshold swing coefficient,  $VT_0$  is the zero bias threshold voltage, VT is the thermal voltage respectively. The  $\eta$ term describes Drain Induced Barrier Lowering (DIBL). Sub-threshold conduction is enhanced by DIBL in which positive V<sub>0</sub> effectively reduces VT. Leakage current doubles for every 8° to 10° rise in temperature. The subthreshold leakage current can be reduced by increasing threshold voltage  $VT_0$ , increasing  $V_{SB}$  and reducing  $V_{GS}$ ,  $V_{DS}$  and lowering the temperature.

Many leakage power control techniques uses the methods such as scaling supply voltage, reducing voltage swing and capacitance, reduction of switching activity or introducing high resistance between the supply voltage and ground. LECTOR [4], GALEOR [5], Sleepy Keeper [6], Sleepy Pass Gate [8] are some of the techniques for leakage reduction. Each method has its own merits and demerits. Some techniques use dual VT transistor; a high VT transistor to reduce leakage and a low VT transistor to improve the speed of operation in critical sections of the

The design and analysis of the LPSR technique is power in data path elements, which makes use of single

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 4, Issue 6, June 2016

VT transistors in all parts of the circuit with the target to achieve low leakage power during sleep mode of operation and lower dynamic power dissipation.

## **II. LITERATURE REVIEW**

The review of earlier work done for leakage reduction and state retention are stated in this section.

A. N. Hanchate and N. Ranganathan

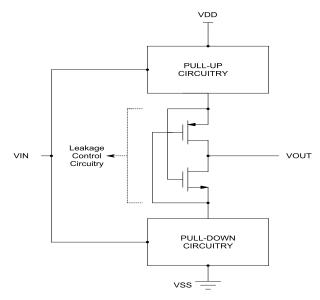

"Lector: A technique for leakage reduction in CMOS circuits". Fig.1 shows the block diagram of Lector technique. In this technique author introduce two leakage control transistors (a p-type and n-type) within the logic circuit for which the gate terminal of each leakage control transistor (LCT) is controlled by the source of the other. In this arrangement, one of the LCTs is always "near its cut-off voltage" for any input combination. This increases the resistance of the path from VDD to ground, leading to significant decrease in leakage currents.

Fig. 1. LECTOR Technique

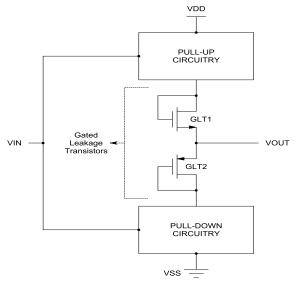

B. Shrikanth Katrue and Dhireesha Kudithipudi

"GALEOR: Leakage reduction for CMOS circuits". Fig.2 shows the block diagram of GALEOR technique. In GALEOR technique the author introduced stacking effect in the circuit results reduction in leakage current flowing across circuit. In this approach, one gate leakage high VT NMOS transistor is introduced between the output and the pull-up network and another gated leakage high VT PMOS transistor is inserted between output and pull-down network. Due to the threshold voltage loss caused by high VT MOS transistors, this technique suffers from significant low voltage swing where low logic level appears much above than 0 and high level occurs much below than VDD. It results higher propagation delay due to low output voltage swing.

These two LECTOR and GALEOR techniques have very good low leak operation but there is no provision of sleep mode of operation.

Fig. 2. GALEOR Technique

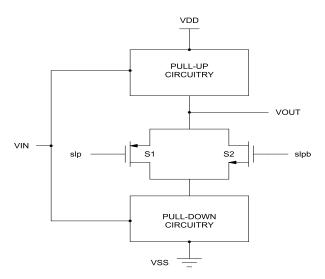

C. M. Geetha Priya, K. Baskaran and D. Krishnaveni "A novel leakage power reduction technique for CMOS VLSI circuits". Fig.3 shows the block diagram of Sleepy Pass Gate technique. In this Sleepy Pass Gate approach author inserted two sleep transistors PMOS and NMOS connected in parallel between pull-up and pull-down networks of a CMOS circuit to form a pass gate like structure. This technique has large power dissipation during pulsed operation.

Fig. 3. Sleepy Pass Gate Technique

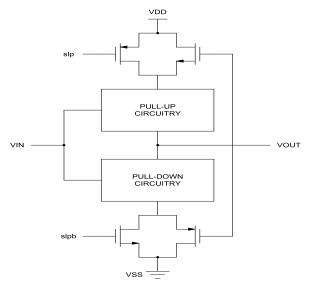

## D. S. H. Kim and V. J. Mooney

"Sleepy keeper: a new approach to low leakage power VLSI design". Fig.4 shows the block diagram of Sleepy Keeper technique. In this work, author inserted parallel connected combination of PMOS and NMOS transistors between pull-up circuitry and supply voltage (VDD), and pull-down circuitry and ground (VSS). In sleep mode, this additional NMOS transistor is the only source of VDD to the pull-up circuitry and additional PMOS transistor is the only source of ground to the pull-down circuitry since the sleep transistor is off. This technique uses extra retention

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 4. Issue 6. June 2016

results in large power dissipation during clocked PMOS transistors in the pull-up and pull-down paths of a operation.

Fig. 4. Sleepy Keeper Approach

#### **III.PREVIOUS WORK**

As per the literature review, even though the above discussed techniques reduce the power dissipation, this techniques are unable to retain state during sleep operation. So, to retain the logical output state even in the sleep mode and to reduce the power consumption to a maximum possible extent a new Low Power State Retention (LPSR) technique is proposed in this paper.

## **IV.PROPOSED METHODOLOGY**

## LPSR Technique:-

The LPSR technique is proposed in this section to reduce the leakage power and total power dissipation to a maximum possible extent.

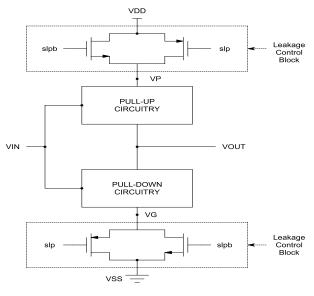

Fig. 5. Generic LPSR Circuit

transistors to maintain logic state during sleep mode but The LPSR technique makes use of a pair of NMOS and CMOS circuit. Fig.5 shows the general block diagram of LPSR circuit.

> The sleep transistor is referred to be either a PMOS or NMOS high VT transistor that connects a permanent power supply (VDD) to the circuit power supply which is commonly called as "virtual power supply". The PMOS transistor is used to switch on VDD and NMOS transistor is used to control VSS supply. The sleep control transistors are controlled by a power management unit to switch ON and OFF power supply.

> As per the literature review, even though the above discussed techniques reduce the power dissipation, this techniques are unable to retain state during sleep operation.

> So, to retain the logical output state even in the sleep mode and to reduce the power consumption to a maximum possible extent a new Low Power State Retention (LPSR) technique is proposed in this paper.

This technique has four modes of operation:

## A. Active Mode

Two sleep control signals namely slp = 0 and slpb = 1 are used to switch on the sleep transistors in leakage control block. Thus the virtual ground node VG is at ground potential and the virtual power node VP is at VDD. The circuit thus sees good potential difference across nodes VP and VG. The circuit functions as per the truth table with good output logic levels.

#### B. Deep Sleep Mode

Both the sleep control signals are held at slp = 1 and slpb= 0 states to switch off all the sleep transistors in both pull up and pull down leakage control blocks. Thus the actual power and ground path are disconnected virtually and the circuit experiences lower voltage across the nodes VP and VG.

A very high resistance path is established between the VDD and VSS due to parallel combination of OFF resistance of sleep transistors and the leakage current flowing through circuit reduces significantly and hence will dissipate lowest power.

## C. State Retention Mode 1

The sleep signals are maintain at slp = 0 and slpb = 0. The circuit sees a voltage higher than ground at the node VG and full VDD at the node VP. The state retention takes place with low leakage current with the output at good logic '1' level.

## D. State Retention Mode 0

The sleep control signals are maintain at slp = 1 and slpb=1. The connection to actual ground is complete, the node VP is at lower VDD. Thus the state retention takes place with low leakage current with the output at good logic '0' level.

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 4. Issue 6. June 2016

## Data Path Elements:-

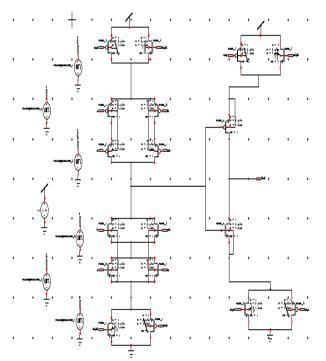

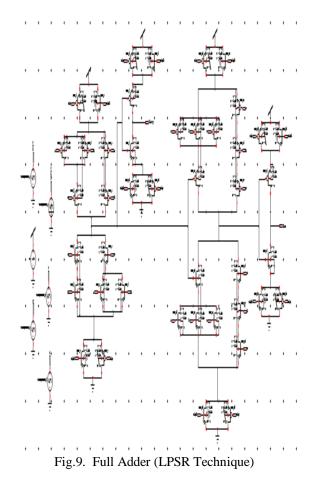

The LPSR technique is applied to 2X1 Multiplexer and techniques. The schematic of the circuits are shown below.

Fig. 6. 2x1 Multiplexer (LPSR Technique)

## V. SIMULATION AND RESULTS

Full Adder. The performance is compared with all other All the data path elements are designed, simulated and functionally verified using 180nm technology files in Tanner EDA tool. Single VT transistors are used in all designs to show the performance benefits and comparison of different techniques. The logical functionality of each design is verified for all input combinations. Static power dissipation is calculated for all input combinations during active and sleep (idle) mode, also dynamic power during clocked operation are all measured using Tanner EDA tools. For pulsed operation transition period is taken as 30µs whereas the static power dissipation is measured for 20 µs duration. All the circuits are controlled by the sleep signals of same pulsed width and period is taken for the purpose of comparison.

> Sleep control signals slp and slpb hold the respective leakage control transistors in the ON state during Active mode and during sleep mode the sleep control signals switch OFF the leakage control transistors.

> The LPSR technique is proposed in this section to reduce the leakage power and total power dissipation to a maximum possible extent. The LPSR technique makes use of a pair of NMOS and PMOS transistors in the pull-up and pull-down paths of a CMOS circuit. Fig.5 shows the general block diagram of LPSR circuit.

> Table I and Table  $\Pi$  provides the dynamic power dissipation, static power dissipation for output logic-1 and logic-0, during active and sleep modes for all 2x1 Multiplexer and Full Adder respectively.

| Technique                        | Dynamic<br>Power<br>Dissipatio<br>n | Static<br>Power<br>Dissipation<br>For Logic 1 | Static Power<br>Dissipation<br>For Logic 0 |

|----------------------------------|-------------------------------------|-----------------------------------------------|--------------------------------------------|

| LECTOR                           | 3.1389µw                            | 75.927pw                                      | 82.389pw                                   |

| GALEOR                           | 8.3809µw                            | 1.0897µw                                      | 0.3331µw                                   |

| Sleepy<br>Keeper<br>sleep mode   | 150.69pw                            | 14.868pw                                      | 53.22pw                                    |

| Sleepy<br>Keeper<br>active mode  | 2.4801µw                            | 100.45pw                                      | 103.30pw                                   |

| Sleepy Pass sleep mode           | 271.34pw                            | 10.129pw                                      | 6.45pw                                     |

| Sleepy Pass active mode          | 3.2457µw                            | 93.969pw                                      | 83.856pw                                   |

| LPSR sleep<br>mode               | 16.255pw                            | 4.2275pw                                      | 10.713pw                                   |

| LPSR<br>active mode              | 2.3129µw                            | 100.45pw                                      | 103.30pw                                   |

| LPSR state<br>retention<br>mode1 | 34.492nw                            | 96.613pw                                      | 61.044pw                                   |

| LPSR state<br>retention<br>mode0 | 40.199nw                            | 59.875pw                                      | 105.62pw                                   |

TABLE I Power Analysis for 2x1 Multiplexer

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 4, Issue 6, June 2016

## TABLE IIIII POWER ANALYSIS FOR FULL ADDER

| Technique                          | Dynamic<br>Power<br>Dissipation | Static<br>Power<br>Dissipation<br>For Logic 1 | Static Power<br>Dissipation<br>For Logic 0 |

|------------------------------------|---------------------------------|-----------------------------------------------|--------------------------------------------|

| LECTOR                             | 8.9959µw                        | 153.67pw                                      | 157.69pw                                   |

| GALEOR                             | 16.257µw                        | 2.0792µw                                      | 0.6064µw                                   |

| Sleepy<br>Keeper<br>sleep mode     | 2.3983nw                        | 165.81pw                                      | 240.64pw                                   |

| Sleepy<br>Keeper<br>active<br>mode | 5.6260µw                        | 196.84pw                                      | 200.64pw                                   |

| Sleepy<br>Pass sleep<br>mode       | 11.368nw                        | 68.897pw                                      | 216.13pw                                   |

| Sleepy<br>Pass active<br>mode      | 8.0353µw                        | 170.92pw                                      | 174.72pw                                   |

| LPSR<br>sleep mode                 | 5.0518nw                        | 76.404pw                                      | 16.185pw                                   |

| LPSR<br>active<br>mode             | 6.6639µw                        | 196.84pw                                      | 200.64pw                                   |

| LPSR state<br>retention<br>mode1   | 84.852nw                        | 181.29pw                                      | 118.34pw                                   |

| LPSR state<br>retention<br>mode0   | 129.14nw                        | 122.22pw                                      | 188.85pw                                   |

## VI. CONCLUSION

LECTOR and GALEOR techniques provide maximum leakage reduction during active mode of operation. But they suffer from maximum power dissipation during pulsed operation as they do not have sleep mode of operation. The Sleepy - Pass Gate technique has large power dissipation during pulsed operation. Though Sleepy Keeper technique maintains state during sleep mode at reduced levels, it results in large power dissipation during pulsed operation because the output terminal is permanently connected to leakage control circuit and there is no deep sleep state. The proposed LPSR technique has active mode static power on par with other techniques and it has least static power dissipation during deep sleep mode and retains state at low power. Thus the LPSR technique provides new choice for the designers of low power CMOS VLSI circuits.

## REFERENCES

- Y. Taur, A. Chandrakasan, W. J. Bowhill, and F. Fox, Eds. Piscataway, "CMOS scaling and issues in sub-0.25 μm systems in Design of High-Performance Microprocessor Circuits," NJ: IEEE, 2001, pp. 27–45.

- [2] Kaushik Roy, Saibal Mukhopadhyay, Hamid Mahmoodi-Meimand, "Leakage Current Mechanisms and Leakage Reduction Techniques in Deep Submicrometer CMOS Circuits," Proceedings of the IEEE, vol. 91, No. 2, February 2003.

- [3] S. Mutoh, T. Douseki, Y. Matsuya, T. Aoki, S. Shigematsu, and J.Yamada, "1-V power supply high-speed digital circuit technology

with multi-threshold voltage CMOS," IEEE J. Solid-State Circuits, vol. 30, pp. 847–854, Aug. 1995.

- [4] N. Hanchate and N. Ranganathan, "Lector: A technique for leakage reduction in CMOS circuits," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 12, no. 2, pp.196-205, February 2004.

- [5] Srikanth Katrue and Dhireesha Kudithipudi,"GALEOR: Leakage reduction for CMOS circuits," 15th IEEE International Conference on Electronics, Circuits and Systems, pp. 574-577, Aug.2008.

- [6] S. H. Kim and V. J. Mooney, "Sleepy keeper: a new approach to low leakage power VLSI design," VLSI-SoC 2006.

- [7] M. Johnson, D. Somasekhar, L.-Y.Chiou, and K. Roy, "Leakage control with efficient use of transistor stacks in single threshold CMOS," IEEE Trans. VLSI Systems., vol. 10, no. 1, pp. 1–5, Feb. 2002.

- [8] M. Geetha Priya, K. Baskaran and D. Krishnaveni, "A Novel Leakage Power Reduction technique for CMOS VLSI Circuits", European Journal of Scientific Research, ISSN 1450-216X Vol.74 No.1 (2012), pp.96-105.